NOR Gate (Verilog)

Jump to navigation

Jump to search

Contents

Synopsis

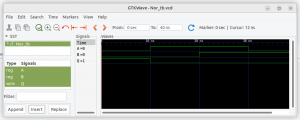

All logic gates can be simplified to a NOR Gate. This is a demonstration of a NOR Gate in Verilog

Notes

I am not an expert, but I discourage using truth tables in Verilog as doing so may defeat optimizations that the compiler may otherwise perform. This is only included as a reference, not as a best practice.

Compilation

iverilog -o Nor_tb.vvp Nor_tb.v

vvp Nor_tb.vvp

gtkwave Nor_tb.vcd

Code Nor.v by assignment

1 module Nor(Q,A,B);

2 output Q;

3 input A,B;

4 assign Q = ~(A | B);

5 endmodule

Code Nor.v by truth table

1 primitive Nor(Q, A, B);

2 output Q;

3 input A,B;

4 table

5 0 0 : 1;

6 0 1 : 0;

7 1 0 : 0;

8 1 1 : 0;

9 x ? : 0;

10 ? x : 0;

11 endtable

12 endprimitive

Code Nor_tb.v test bench

1 `timescale 1ns/1ns

2 `include "Nor.v"

3

4 module Nor_tb;

5

6 reg A;

7 reg B;

8 wire Q;

9

10 Nor uut(Q,A,B);

11

12 initial begin

13 $dumpfile("Nor_tb.vcd");

14 $dumpvars(0,Nor_tb);

15

16 A = 0;

17 B = 0;

18 #10;

19 A = 1;

20 #10;

21 B = 1;

22 #10;

23 A = 0;

24 #10;

25

26 $display("Test Complete!");

27 end

28 endmodule